CMU 18-447 5'09 L11-1 © 2009 J. C. Hoe

# 18-447 Lecture 11: Pipelined Implementations: Hazards and Resolutions

James C. Hoe Dept of ECE, CMU February 25, 2009

Announcements: Project 1 due this week

Handouts:

Electrical & Computer

CMU 18-447 S'09 L11-2 © 2009

# Instruction Pipeline Reality

- Identical operations ... NOT!

- $\Rightarrow$  unifying instruction types

- coalescing instruction types into one "multi-function" pipe

- external fragmentation (some idle stages)

- Uniform Suboperations ... NOT!

- $\Rightarrow$  balance pipeline stages

- stage quantization to yield balanced stages

- internal fragmentation (some too-fast stages )

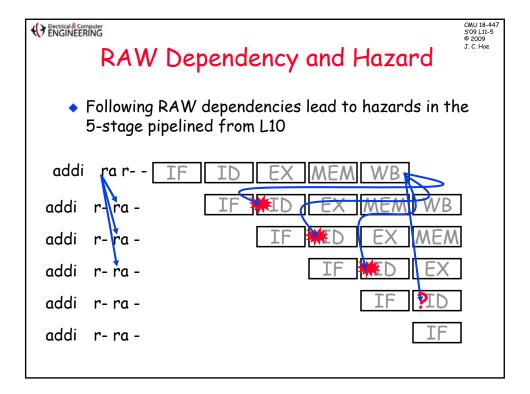

- Independent operations ... NOT!

- ⇒ resolve data and resource hazards

- duplicate contended resources

- inter-instruction dependency detection and resolution

MIPS ISA features are engineered for improved pipelineability

CMU 18-447 5'09 L11-3 © 2009

# Data Dependence

Data dependence

$$r_3 \leftarrow r_1 \text{ op } r_2$$

$r_5 \leftarrow r_2 \text{ op } r_4$

$r_3 \leftarrow r_1 \text{ op } r_2$  Read-after-Write  $r_5 \leftarrow r_3 \text{ op } r_4$  (RAW)

Anti-dependence

$$r_3 \leftarrow r_1 \text{ op } r_2$$

Write-after  $r_1 \leftarrow r_4 \text{ op } r_5$  (WAR)

$r_3 \leftarrow r_1$  op  $r_2$  Write-after-Read

Output-dependence

$$r_3 \leftarrow r_1 \text{ op } r_2$$

Write-after-Write  $r_5 \leftarrow r_3 \text{ op } r_4$  (WAW)  $r_3 \leftarrow r_6 \text{ op } r_7$

We discuss control-flow dependence in a later lecture

Electrical & Computer ENGINEERING

# Dependencies and Pipelined Execution

Sequential and atomic instruction semantics

The true dependence between two instructions may only require ordering of certain sub-operations

This semantics is an overspecification. It defines what is correct but doesn't say to do it that way only

# ## ENGINEERING Computer CMU 18: 5:09 L11: 0 0 2:09 ## 2:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ## 3:09 ##

# Register Data Hazard Analysis

|     | R/I-<br>Type | LW       | SW      | Br      | J | Jr      |

|-----|--------------|----------|---------|---------|---|---------|

| IF  |              |          |         |         |   |         |

| ID  | read RF      | read RF  | read RF | read RF |   | read RF |

| EX  |              |          |         |         |   |         |

| MEM |              |          |         |         |   |         |

| WB  | write RF     | write RF |         |         |   |         |

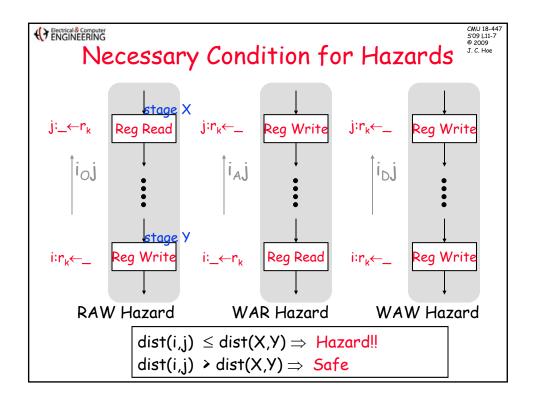

- For a given pipeline, when is there a register data hazard between 2 data dependent instructions?

- dependence type: RAW, WAR, WAW?

- instruction types involved?

- distance between the two instructions?

#### CMU 18-447 S'09 L11-8 © 2009

# RAW Hazard Analysis Example

|     | R/I-<br>Type | LW       | SW      | Br      | J | Jr      |

|-----|--------------|----------|---------|---------|---|---------|

| IF  |              |          |         |         |   |         |

| ID  | read RF      | read RF  | read RF | read RF |   | read RF |

| EX  |              |          |         |         |   |         |

| MEM |              |          |         |         |   |         |

| WB  | write RF     | write RF |         |         |   |         |

- Instructions I<sub>A</sub> and I<sub>B</sub> (where I<sub>A</sub> comes before I<sub>B</sub>)

have RAW hazard iff

- $I_B$  (R/I, LW, SW, Br or JR) reads a register written by  $I_A$  (R/I or LW)

- $dist(I_A, I_B) \le dist(ID, WB) = 3$

What about WAW and WAR hazard? What about memory data hazard?

| Electrical Computer ENGINEERING |     |    |                |    |     |     |                       |                | CMU 18-447<br>S'09 L11-11<br>© 2009 |                |                 |                 |  |

|---------------------------------|-----|----|----------------|----|-----|-----|-----------------------|----------------|-------------------------------------|----------------|-----------------|-----------------|--|

| Pipeline Stall                  |     |    |                |    |     |     |                       |                |                                     | J. C. Hoe      |                 |                 |  |

|                                 |     |    |                |    |     |     |                       |                |                                     |                | 1               |                 |  |

|                                 |     | †0 | † <sub>1</sub> | †2 | †3  | †4  | <b>†</b> <sub>5</sub> | † <sub>6</sub> | <b>†</b> <sub>7</sub>               | † <sub>8</sub> | <b>†</b> 9      | † <sub>10</sub> |  |

|                                 | IF  | -  | j              | k  | k   | k   | k                     | ı              |                                     |                |                 |                 |  |

|                                 | ID  | h  | i              | j  | j   | j   | j                     | k              | I                                   |                |                 |                 |  |

|                                 | EX  |    | h              | i  | bub | bub | bub                   | j              | k                                   | ı              |                 |                 |  |

|                                 | MEM |    |                | h  | i   | bub | bub                   | bub            | j                                   | k              | I               |                 |  |

|                                 | WB  |    |                |    | h   | i/  | bub                   | bub            | bub                                 | j              | k               | ı               |  |

| i: rx ← _                       |     |    |                |    |     |     |                       |                | -                                   |                |                 |                 |  |

|                                 |     |    |                |    |     |     |                       |                | <u>J:</u>                           | <u> </u>       | <u> - r&gt;</u> | •               |  |

## ENGINEERING CMU 18-447

\*\*S09 L11-13

\*\*D 2009

\*\*I C Hope

\*\*T C Hope

\*\*T

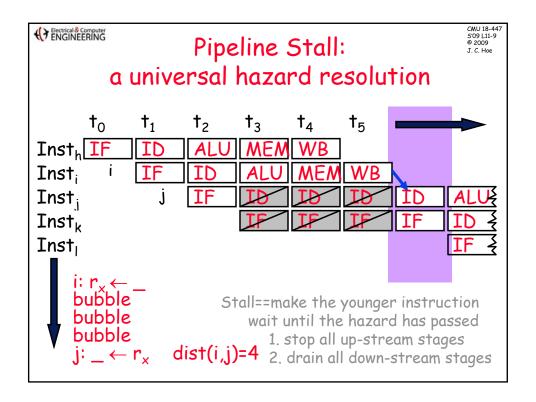

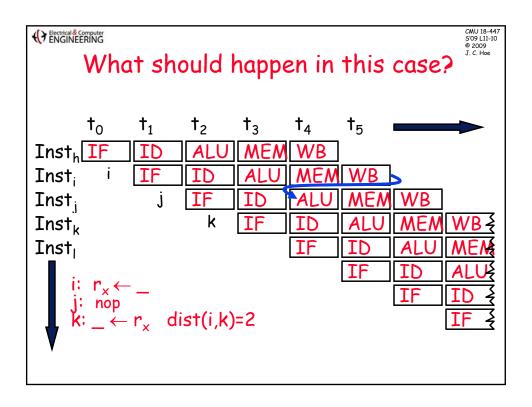

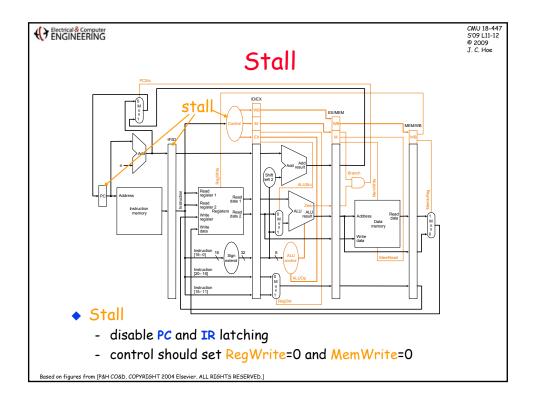

## Stall Conditions

- Instructions I<sub>A</sub> and I<sub>B</sub> (where I<sub>A</sub> comes before I<sub>B</sub>)

have RAW hazard iff

- $I_B$  (R/I, LW, SW, Br or JR) reads a register written by  $I_A$  (R/I or LW)

- $dist(I_A, I_B) \le dist(ID, WB) = 3$

- In other words, must stall when I<sub>B</sub> in ID stage wants to read a register to be written by I<sub>A</sub> in EX, MEM or WB stage

Electrical & Computer

CMU 18-447 S'09 L11-14 © 2009

## Stall Condition

- Helper functions

- rs(I) returns the rs field of I

- use\_rs(I) returns true if I requires RF[rs] and rs!=r0

- Stall when

```

\begin{array}{lll} - & (rs(\mathbf{IR_{ID}}) = = dest_{EX}) \; \&\& \; use\_rs(\mathbf{IR_{ID}}) \; \&\& \; RegWrite_{EX} & \text{or} \\ - & (rs(\mathbf{IR_{ID}}) = = dest_{MEM}) \; \&\& \; use\_rs(\mathbf{IR_{ID}}) \; \&\& \; RegWrite_{MEM} & \text{or} \\ - & (rs(\mathbf{IR_{ID}}) = = dest_{WB}) \; \&\& \; use\_rs(\mathbf{IR_{ID}}) \; \&\& \; RegWrite_{WB} & \text{or} \\ - & (rt(\mathbf{IR_{ID}}) = = dest_{EX}) \; \&\& \; use\_rt(\mathbf{IR_{ID}}) \; \&\& \; RegWrite_{EX} & \text{or} \\ - & (rt(\mathbf{IR_{ID}}) = = dest_{MEM}) \; \&\& \; use\_rt(\mathbf{IR_{ID}}) \; \&\& \; RegWrite_{MEM} & \text{or} \\ - & (rt(\mathbf{IR_{ID}}) = = dest_{WB}) \; \&\& \; use\_rt(\mathbf{IR_{ID}}) \; \&\& \; RegWrite_{WB} & \end{array}

```

It is crucial that the EX, MEM and WB stages continue to advance normally during stall cycles

CMU 18-447 5'09 L11-15 © 2009 J. C. Hoe

### Electrical & Computer ENGINEERING

# Impact of Stall on Performance

- Each stall cycle corresponds to 1 lost ALU cycle

- For a program with N instructions and S stall cycles, Average IPC=N/(N+S)

- S depends on

- frequency of RAW hazards

- exact distance between the hazard-causing instructions

- distance between hazards

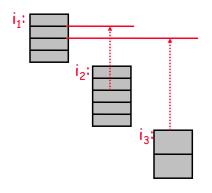

suppose i<sub>1</sub>,i<sub>2</sub> and i<sub>3</sub> all depend on i<sub>0</sub>, once i<sub>1</sub>'s hazard is resolved, i<sub>2</sub> and i<sub>3</sub> must be okay too

```

Electrical & Computer ENGINEERING

Sample Assembly [p126, P&H]

for (j=i-1; j>=0 && v[j] > v[j+1]; j-=1) { ..... }

addi

$s1, $s0, -1

3 stalls

for2tst:

slti

$t0, $s1, 0

3 stalls

bne

$t0, $zero, exit2

sll

$t1, $s1, 2

3 stalls

add

$t2, $a0, $t1

3 stalls

$13,0($12)

lw

$†4, 4($†2)

lw

3 stalls

slt

$t0, $t4, $t3

3 stalls

beg

$t0, $zero, exit2

$s1, $s1, -1

addi

for2tst

exit2:

```

CMU 18-447 S'09 L11-17 © 2009 J. C. Hoe

# Data Forwarding or Register Bypassing

- It is intuitive to think of RF as state

- "add rx ry rz" literally means get values from RF[ry] and RF[rz] respectively and put result in RF[rx]

- But, RF is just a part of a computing abstraction

- "add rx ry rz" means 1. get the results of the last instructions to define the values of RF[ry] and RF[rz], respectively, and 2. until another instruction redefines RF[rx], younger instructions that refers to RF[rx] should use this instruction's result

- What matters is to maintain the correct "dataflow" between operations, thus

add ra r- r- IF ID EX MEM WB addi r- ra r-

Electrical & Computer ENGINEERING

CMU 18-44 5'09 L11-18 © 2009

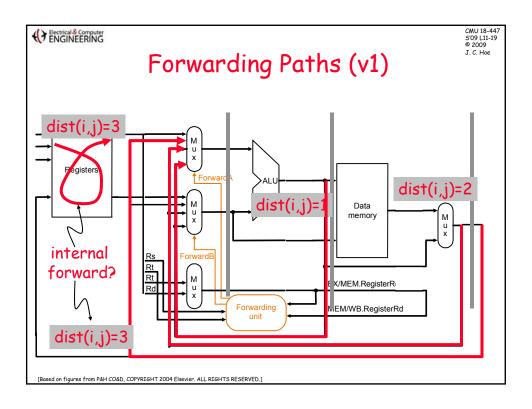

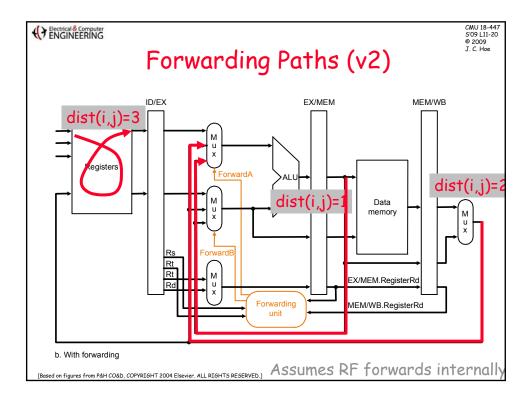

# Resolving RAW Hazard by Forwarding

- Instructions I<sub>A</sub> and I<sub>B</sub> (where I<sub>A</sub> comes before I<sub>B</sub>)

have RAW hazard iff

- $I_B$  (R/I, LW, SW, Br or JR) reads a register written by  $I_A$  (R/I or LW)

- $dist(I_A, I_B) \le dist(ID, WB) = 3$

- In other words, if I<sub>B</sub> in ID stage reads a register written by I<sub>A</sub> in EX, MEM or WB stage, then the operand required by I<sub>B</sub> is not yet in RF

- $\Rightarrow$  retrieve operand from datapath instead of the RF

- ⇒ retrieve operand from the youngest definition if multiple definitions are outstanding

CMU 18-447 5'09 L11-21 © 2009 J. C. Hoe

# Forwarding Logic (for v2)

if  $(rs_{EX}!=0)$  &&  $(rs_{EX}==dest_{MEM})$  && RegWrite\_{MEM} then forward operand from MEM stage // dist=1 else if  $(rs_{EX}!=0)$  &&  $(rs_{EX}==dest_{WB})$  && RegWrite\_{WB} then forward operand from WB stage // dist=2 else

use  $A_{EX}$  (operand from register file) // dist >= 3

Ordering matters!! Must check youngest match first

Why doesn't **use\_rs()** appear in the forwarding logic?

#### Electrical & Computer ENGINEERING

CMU 18-44 5'09 L11-22 © 2009

# Data Hazard Analysis (with Forwarding)

|     | R/I-<br>Type   | LW      | SW    | Br  | J | Jr  |

|-----|----------------|---------|-------|-----|---|-----|

| IF  |                |         |       |     |   |     |

| ID  |                |         |       |     |   | use |

| EX  | use<br>produce | use     | use   | use |   |     |

| MEM |                | produce | (use) |     |   |     |

| WB  |                |         |       |     |   |     |

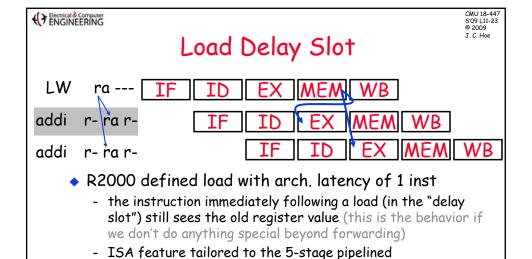

Even with data-forwarding, RAW dependence on an immediate preceding LW instruction produces a hazard

- microarchitecture Warning!! Implementation exposed!!

If loads are defined normally, i.e., atomic

- a dependent immediate successor to LW must stall 1 cycle in ID

- Stall = (rs(IR<sub>ID</sub>)==dest<sub>EX</sub>) && use\_rs(IR<sub>ID</sub>) && MemRead<sub>EX</sub>

```

Electrical & Computer ENGINEERING

Sample Assembly [p126, P&H]

for (j=i-1; j>=0 && v[j] > v[j+1]; j-=1) { ......}

addi

$s1, $s0, -1

for2tst:

slti

$t0, $s1, 0

$t0, $zero, exit2

bne

sll

$t1, $s1, 2

add

$t2,$a0,$t1

lw

$\,\tag{3}\,0(\$\tag{2})

$†4, 4($†2)

lw

nop

slt

$t0, $t4, $t3

$t0, $zero, exit2

beg

......

$s1, $s1, -1

addi

for2tst

exit2:

```

CMU 18-447 S'09 L11-25 © 2009 J. C. Hoe

# Terminology

- Dependencies

- ordering requirement between instructions

- ◆ Pipeline Hazards:

- (potential) violations of dependencies

- Hazard Resolution:

- static ⇒ schedule instructions at compile time to avoid hazards

- dynamic ⇒ detect hazard and adjust pipeline operation

Stall, Flush or Forward

- Pipeline Interlock:

- hardware mechanisms for dynamic hazard resolution

- detect and enforce dependences at run time

Electrical Computer

CMU 18-447 5'09 L11-26 © 2009

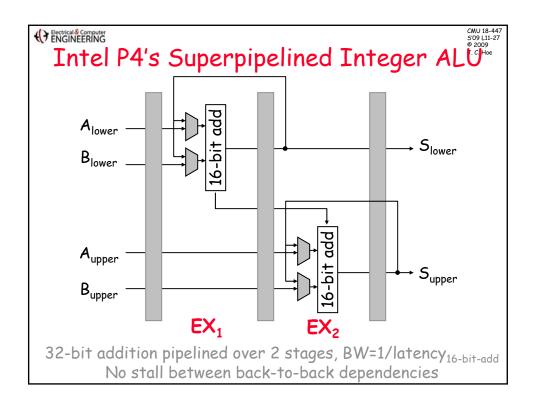

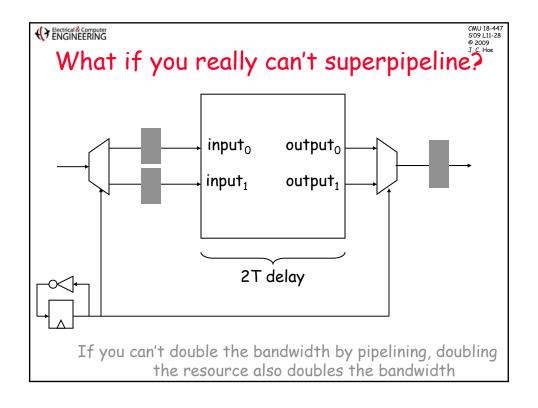

# Why not very deep pipelines?

- 5-stage pipeline still has plenty of combinational delay between registers

- "Superpipelining" ⇒ increase pipelining such that even intrinsic operations (e.g. ALU, RF access, memory access) require multiple stages

- What's the problem?

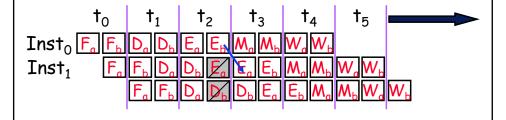

$Inst_0: r1 \leftarrow r2 + r3$

$Inst_1$ : r4  $\leftarrow$  r1 + 2