### EDA技术实用教程课后答案解析

#### 习题四

**习题4-5:** 列表详细说明MAX+plusII中prim.mf和mega_lpm库中的内容和用法。

- **prim库**:包含了基本的电子元件,如逻辑门(AND、OR、NOT等)、触发器(D触发器、JK触发器等)以及其他基本组件,这些组件构成了电路设计的基础。

- **mf库**:主要包含了一系列74系列芯片的逻辑元件模型,如74LS00(双输入四或非门)、74LS04(六反相器)等,这些元件模型可以帮助设计者快速构建复杂的数字逻辑电路。

- **mega_lpm库**:提供了参数可定制的复杂逻辑元件,例如LPM_ADDER(加法器)、LPM_MUX(多路选择器)等,这些元件可以根据设计需求调整参数,提高了设计的灵活性。

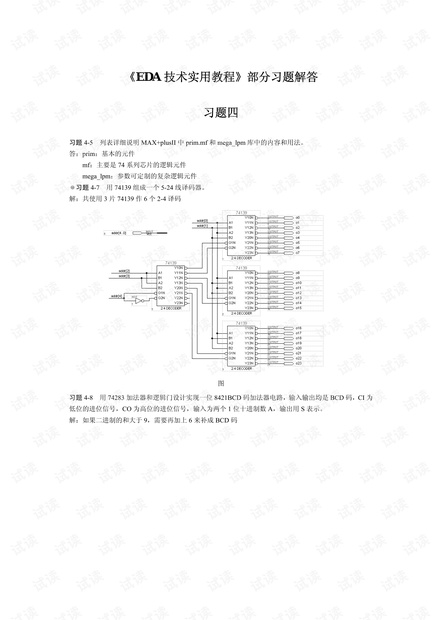

**习题4-7:** 用74139组成一个5-24线译码器。

- **解决方案**:为了实现这个任务,可以使用3片74139芯片来构建6个2-4线译码器。74139是一种2-4线译码器芯片,可以通过扩展的方式将其组合起来实现更大的译码功能。具体步骤如下:

- 使用第一片74139作为最高位的2-4线译码器。

- 使用第二片和第三片74139连接起来作为次高位的2-4线译码器。

- 将这三个2-4线译码器的输出组合在一起,形成一个完整的5-24线译码器。

**习题4-8:** 用74283加法器和逻辑门设计实现一位8421BCD码加法器电路,输入输出均是BCD码,CI为低位的进位信号,CO为高位的进位信号,输入为两个1位十进制数A,输出用S表示。

- **解决方案**:当两个二进制数相加的结果超过9时,需要加上6(即0110B),使其变成正确的BCD码。设计过程如下:

- 使用74283加法器进行两个二进制数的加法运算。

- 如果加法器的输出大于9,则加上6进行修正。

- CI和CO分别表示低位和高位的进位信号。

- 输出S为最终的BCD码。

**习题4-9:** 设计一个7人表决电路,参加表决者7人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮;表决不通过则红指示灯亮。

- **解决方案**:可以通过以下步骤设计该电路:

- 使用7个输入端,每个输入端代表一个表决者的投票(1表示同意,0表示不同意)。

- 通过多个1位全加器计算所有同意的票数总和。

- 如果总和大于等于4(即一半以上的人同意),则绿指示灯亮,表示表决通过;否则红指示灯亮,表示表决未通过。

**习题4-10:** 使用prim和mf库中的元件设计一个周期性产生二进制序列01001011001的序列发生器,用移位寄存器或用同步时序电路实现,并用时序仿真器验证其功能。

- **解决方案**:一种可能的设计方法是使用移位寄存器来实现该序列发生器:

- 设计一个移位寄存器,初始值设为序列的第一个值。

- 在时钟信号的作用下,每次将移位寄存器中的内容右移一位,并将最右边的一位作为下一个值的输入。

- 通过这种方式,可以周期性地产生所需的序列。

- 使用时序仿真器验证其功能,确保输出序列正确无误。

**习题4-11:** 用D触发器设计3位二进制加法计数器。

- **解决方案**:设计3位二进制加法计数器需要注意以下几点:

- 使用三个D触发器级联,每个触发器的输出作为下一个触发器的输入。

- 当最后一个触发器的状态改变时,表示计数器完成了一次计数。

- 注意D触发器级联时应取非端,否则只能作分频器。

**习题4-12:** 用D触发器构成按循环码(000->001->011->111->101->100->000)规律工作的六进制同步计数器。

- **解决方案**:为了按照给定的循环码顺序工作,需要考虑不同状态时D触发器输入端的值。根据题目要求,可以构建如下表格来确定每个D触发器的输入值:

- Q2Q1Q0:当前状态

- D2D1D0:下一个状态

- 例如,从000到001,D2=0, D1=0, D0=1。

通过以上分析,我们可以更深入地理解EDA技术中的关键概念和技术细节,这些练习题不仅帮助我们巩固了基础知识,还提升了我们解决实际问题的能力。

- 1

- 2

- 3

前往页