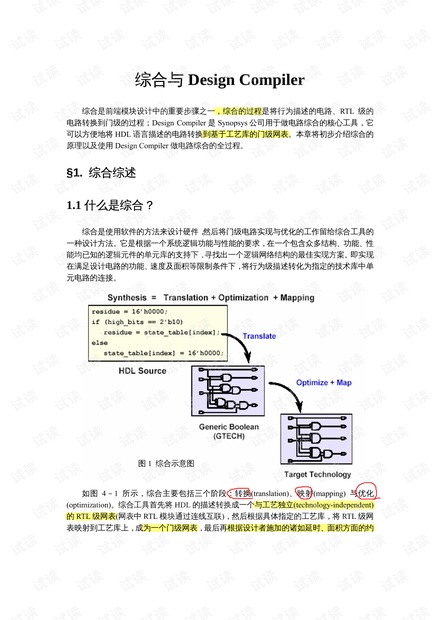

"综合与Design Compiler" 综合是前端模块设计中的重要步骤之一,综合的过程是将行为描述的电路、RTL 级的电路转换到门级的过程。Design Compiler 是 Synopsys 公司用于做电路综合的核心工具,它可以方便地将 HDL 语言描述的电路转换到基于工艺库的门级网表。 综合的原理是使用软件的方法来设计硬件,然后将门级电路实现与优化的工作留给综合工具的一种设计方法。它是根据一个系统逻辑功能与性能的要求,在一个包含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑网络结构的最佳实现方案。即实现在满足设计电路的功能、速度及面积等限制条件下,将行为级描述转化为指定的技术库中单元电路的连接。 综合主要包括三个阶段:转换、映射与优化。综合工具首先将 HDL 的描述转换成一个与工艺独立的 RTL 级网表,然后根据具体指定的工艺库,将 RTL 级网表映射到工艺库上,成为一个门级网表,最后再根据设计者施加的诸如延时、面积方面的约束条件,对门级网表进行优化。 在设计的不同的抽象层次中,设计者可以在上述的三个层次用 HDL 语言描述他的设计,根据 HDL 语言描述的层次的高低,综合也相应的可以分为逻辑级综合、RTL 级综合以及行为级综合。 逻辑级综合中,设计被描述成布尔等式的形式,触发器、锁存器这样的基本单元采用元件例化的方式表达出来。RTL 级综合中,电路的数学运算和行为功能分别通过 HDL 语言特定的运算符和行为结构描述出来。行为级综合比 RTL 级综合层次更高,同时它描述电路也越抽象,在 RTL 级中,电路在每个时钟边沿的行为必须确切的描述出来,而行为级描述却不是这样,这里没有明确规定电路的时钟周期,推断法则也不是用来推断寄存器。 Design Compiler 是一个功能强大且灵活的电路综合工具,可以帮助设计者快速实现电路设计,并且可以根据设计者的需求进行优化,提高设计效率和设计质量。

剩余115页未读,继续阅读

- 粉丝: 0

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 大数据视野下易筋养生术的运用及推广.docx

- 绘制球体的SphereSceneNode类.doc

- 分布式核心DevOps平台概要设计.docx

- WEB的管理开题.doc

- 塔架监造检验项目管理及检验方法.doc

- 移动通信技术的发展及热点分析.doc

- XX物业项目管理的整体设计与构思.doc

- CentOS-Docker安装指南.doc

- 议网络信息技术在教学中的应用.docx

- 课堂讲义同步系列高中数学北师大版必修三课件:第二章算法初步(22)变量与赋值.ppt

- 济职设备自动化人才培养方案.doc

- plc自动售货机大学设计.doc

- 互联网+教育背景下的初中英语教学策略.docx

- 网站策划方案参考.docx

- 物料分拣控制系统的设计(PLC).docx

- 计算机工程写作指导.doc

信息提交成功

信息提交成功