从给定的文件标题、描述、标签以及部分内容中,我们可以提炼出以下IT行业,特别是集成电路设计领域的关键知识点:

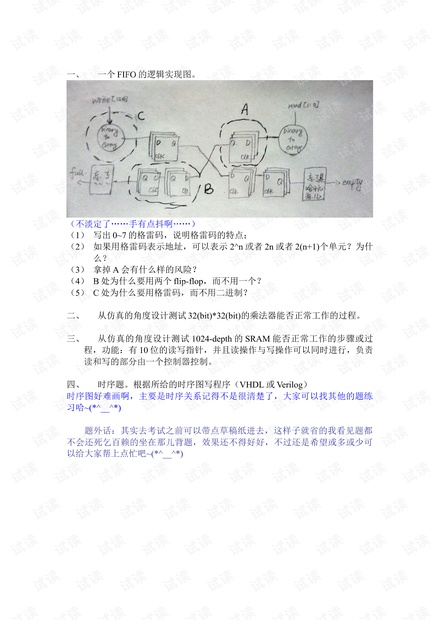

### 1. FIFO逻辑实现

- **FIFO(First In First Out)**,即“先进先出”队列,在数字电路设计中是一种常用的存储结构,用于在数据流中保持数据的顺序。其主要作用是缓存数据,确保数据在不同速率的系统间传输时不会丢失。

### 2. 格雷码的应用与特点

- **格雷码**是一种二进制数字系统中使用的编码方式,其特点是任意两个相邻的数值仅有一位二进制位不同。这一特性使得它在数字电路设计中特别适用于减少切换错误,因为在切换过程中只有一位变化,减少了干扰的可能性。

- 格雷码可以表示2^n个单元,这是因为它的每一位都独立于其他位,因此每增加一位就可以表示两倍的单元数量,类似于二进制编码。

### 3. 风险评估

- 在数字电路设计中,**拿掉A**可能指的是移除某个关键组件或信号路径,这将直接影响到电路的功能完整性,可能导致数据丢失、误码率增加或是整个系统性能下降等问题。风险评估是设计过程中的关键步骤,旨在预测并最小化潜在问题。

### 4. 双翻转器的作用

- 使用两个**flip-flop(触发器)**而不是一个,通常是为了实现更复杂的功能,比如数据锁存、错误检测或是创建复杂的时序逻辑。双触发器可以构建如JK触发器、D触发器等,增强电路的稳定性和可靠性。

### 5. 格雷码优于二进制的原因

- 在某些应用场景下,如地址编码或数据传输,使用格雷码而非二进制可以减少信号切换次数,从而降低电磁干扰和功耗,提高数据传输的准确性。这是因为格雷码在转换过程中仅改变一位,降低了多比特同时切换的风险。

### 6. 仿真测试设计

- **仿真测试**是验证数字电路设计是否正确的重要手段,包括对乘法器和SRAM等复杂组件的测试。设计测试过程需要考虑输入输出信号、时序关系、边界条件等多个方面,以确保电路在各种工作条件下都能正常运行。

### 7. SRAM功能与测试

- **SRAM(Static Random Access Memory)**是一种静态随机存取存储器,具有快速访问和无需刷新的优点。对于1024-depth的SRAM,测试需覆盖其读写功能、读写指针的控制逻辑、同时读写操作的能力以及控制器的协调机制,确保数据的准确读取和写入。

### 8. 时序编程

- 时序编程涉及根据时序图编写VHDL或Verilog代码,以实现特定的时序逻辑。这要求设计师深入理解时钟信号、同步异步电路的工作原理以及如何通过代码表达这些时序关系,确保电路的时序特性满足设计需求。

### 结论

综合以上分析,联发科技的数字IC设计笔试题涵盖了从基本的编码方式、电路设计原理到高级的仿真测试技术等广泛的知识领域,对考生的理论知识和实践能力提出了全面的考验。准备此类考试不仅需要扎实的基础理论知识,还需要丰富的实践经验和创新思维,以便在实际设计中灵活运用各种技术和策略,解决复杂的设计挑战。