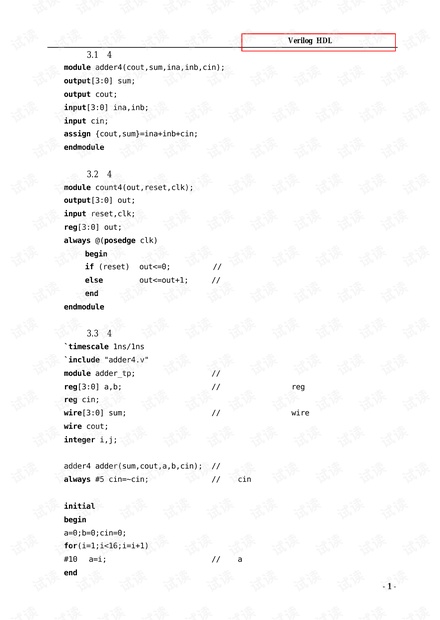

### Verilog HDL基础知识及应用实例解析 #### 一、Verilog HDL简介 Verilog是一种硬件描述语言(Hardware Description Language, HDL),主要用于数字电路的设计、验证和文档记录。它能够描述数字系统的结构、行为以及定时特性,并支持从系统级到门级的设计。 #### 二、Verilog经典设计实例分析 ##### 1. 4位全加器 (Example 3.1) **模块定义:** `adder4` 模块包含两个4位输入向量 `ina` 和 `inb`,一个输入 `cin`(进位),以及一个4位输出向量 `sum` 和一个输出 `cout`(进位)。 **代码实现:** ```verilog module adder4(cout, sum, ina, inb, cin); output [3:0] sum; output cout; input [3:0] ina, inb; input cin; assign {cout, sum} = ina + inb + cin; endmodule ``` - **功能:** 实现4位二进制数的加法运算。 - **实现方式:** 使用 `assign` 语句直接计算输入向量的和,并将结果分配给 `sum` 和 `cout`。 ##### 2. 4位计数器 (Example 3.2) **模块定义:** `count4` 模块包含一个4位输出向量 `out`,一个复位信号 `reset` 和一个时钟信号 `clk`。 **代码实现:** ```verilog module count4(out, reset, clk); output [3:0] out; input reset, clk; reg [3:0] out; always @(posedge clk) begin if (reset) out <= 0; // 同步复位 else out <= out + 1; // 计数 end endmodule ``` - **功能:** 实现一个4位的同步计数器。 - **实现方式:** 使用 `always` 块在时钟上升沿进行操作,通过 `if` 语句实现同步复位。 ##### 3. 4位全加器的仿真程序 (Example 3.3) **仿真环境构建:** ```verilog `timescale 1ns / 1ns `include "adder4.v" module adder_tp; reg [3:0] a, b; reg cin; wire [3:0] sum; wire cout; integer i, j; adder4 adder(sum, cout, a, b, cin); always #5 cin = ~cin; initial begin a = 0; b = 0; cin = 0; for (i = 1; i < 16; i = i + 1) #10 a = i; end initial begin for (j = 1; j < 16; j = j + 1) #10 b = j; end initial $monitor($time, "%d + %d + %b = {%b, %d}", a, b, cin, cout, sum); #160 $finish; end endmodule ``` - **功能:** 该仿真程序用于验证4位全加器的功能正确性。 - **实现方式:** 使用 `initial` 块初始化输入值,并通过循环改变输入值进行测试;使用 `always` 块模拟时序信号的变化;使用 `$monitor` 函数监控并打印输出结果。 ##### 4. 4位计数器的仿真程序 (Example 3.4) **仿真环境构建:** ```verilog `timescale 1ns / 1ns `include "count4.v" module coun4_tp; reg clk, reset; wire [3:0] out; parameter DELY = 100; count4 mycount(out, reset, clk); always #(DELY / 2) clk = ~clk; initial begin clk = 0; reset = 0; #DELY reset = 1; #DELY reset = 0; #(DELY * 20) $finish; end initial $monitor($time, "clk = %d reset = %d out = %d", clk, reset, out); endmodule ``` - **功能:** 验证4位计数器的正确性。 - **实现方式:** 类似于4位全加器的仿真程序,但主要关注计数器的时序特性和复位功能。 ##### 5. “与-或-非”门电路 (Example 3.5) **模块定义:** `AOI` 模块包含四个输入 `A`, `B`, `C`, `D` 和一个输出 `F`。 **代码实现:** ```verilog module AOI(A, B, C, D, F); input A, B, C, D; output F; wire F; assign F = ~( (A & B) | (C & D) ); endmodule ``` - **功能:** 实现了一个与-或-非逻辑门电路。 - **实现方式:** 使用 `assign` 语句直接计算逻辑函数的结果。 ##### 6. 用case语句描述的4选1数据选择器 (Example 5.1) **模块定义:** `mux4_1` 模块包含四个输入 `in0`, `in1`, `in2`, `in3` 和一个选择信号 `sel`。 **代码实现:** ```verilog module mux4_1(out, in0, in1, in2, in3, sel); output out; input in0, in1, in2, in3; input [1:0] sel; reg out; always @(in0 or in1 or in2 or in3 or sel) case (sel) 2'b00: out = in0; 2'b01: out = in1; 2'b10: out = in2; 2'b11: out = in3; default: out = 2'bx; endcase endmodule ``` - **功能:** 实现一个4选1的数据选择器。 - **实现方式:** 使用 `case` 语句根据选择信号 `sel` 的值选择输出。 ##### 7. 同步置数、同步清零的计数器 (Example 5.2) **模块定义:** `count` 模块包含一个8位输出 `out`,一个8位数据输入 `data`,一个加载信号 `load`,一个复位信号 `reset` 和一个时钟信号 `clk`。 **代码实现:** ```verilog module count(out, data, load, reset, clk); output [7:0] out; input [7:0] data; input load, clk, reset; reg [7:0] out; always @(posedge clk) begin if (!reset) out = 8'h00; // 同步清0,低电平有效 else if (load) out = data; // 同步预置 else out = out + 1; // 计数 end endmodule ``` - **功能:** 实现了一个具有同步置数和同步清零功能的8位计数器。 - **实现方式:** 在时钟上升沿执行操作,通过 `if` 语句实现同步置数和同步清零功能。 ##### 8. 用always过程语句描述的简单算术逻辑单元 (Example 5.3) **模块定义:** 简单算术逻辑单元模块定义未给出完整代码,但从提供的宏定义可以看出,该模块可能包含多个功能选项,如加法和减法。 以上八个例子展示了Verilog HDL在数字电路设计中的广泛应用,从基本的组合逻辑电路到复杂的时序逻辑电路,以及它们的仿真验证。通过这些例子的学习,可以深入了解Verilog HDL的基本语法和高级特性,为进一步深入学习数字电路设计打下坚实的基础。

剩余82页未读,继续阅读

csdv20122015-11-17整理得还行。

csdv20122015-11-17整理得还行。

- 粉丝: 37

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- Git版本控制从入门到实战:完整教程与源码解析,掌握团队协作开发技巧

- kafka面试题及答案PDF

- 【后台管理系统】图床链接在后台配置中的应用:简化操作与多端同步及安全管理优化方案设计

- FLAC耦合PFC3D,静力触探模拟与CPT

- 储能系统双向DCDC变换器蓄电池充放电Buck与Boost模式仿真模型研究:维持直流母线电压平衡的策略

- 修复版运营级新ui口红机源码

- 电机控制系统:基于Maxwell与SimP Lor联合仿真的矢量控制SVPWM算法实践 终极版

- 【后台管理系统】基于图床链接的图标资源管理方案:简化操作与多端同步应用

- Linux网络编程实战指南

- 光储直流微电网Simulink仿真:双向变换器与MPPT能量管理策略

- 分析系统聚类主题分析可视化分析

- GPT-5核心技术解析与实战应用教程:从原理到源码实现

- Maxwell与OptiSLang在永磁电机多物理场计算及多目标优化中的应用 - 振动噪声仿真 文档

- 四轮独立驱动电动汽车侧偏刚度估计:基于Cars im与CKF算法的S函数实现及应用

- C#+WPF运动控制路径算法框架:适用于多种工控设备的绘图控件与模板源码

- springboot-高校毕业与学位资格审核系统(源码+sql脚本).zip

信息提交成功

信息提交成功